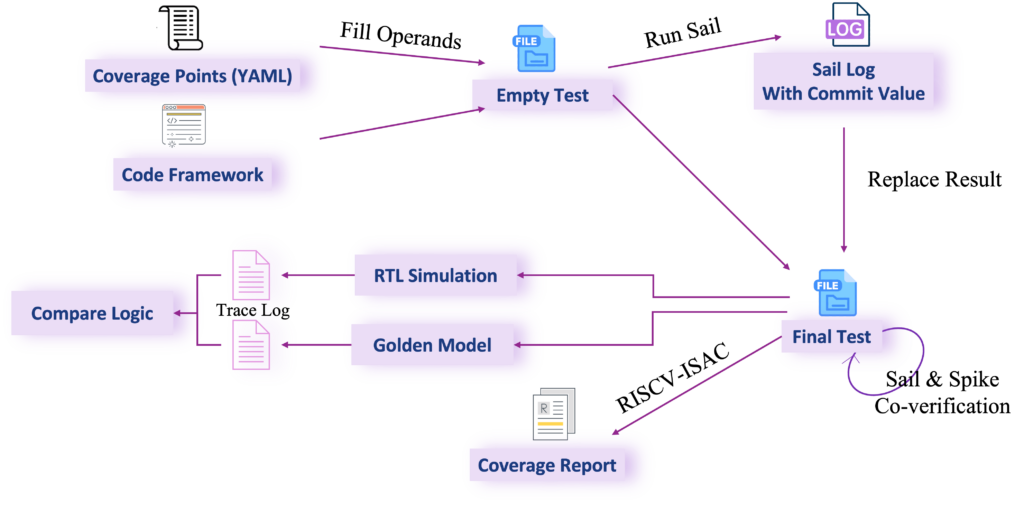

RIOS Lab cooperate with the RISC-V foundation and design a configurable RVV test generator for the RISC-V community. We first designed and implemented the RVV Sail Model as the golden model to execute the RVV instructions. We also employ Spike for cross-validation of RVV program executions as compared to our Sail model. After massive iterations of RVV instruction tests, we ensure the correctness of our introduced Sail Model. We have issued pull requests to the official RISC-V Sail Model and our effort is partly upstream now.

With the Sail model support, we further developed a configurable test generator with quantifiable coverage for RISC-V Vector Extension. The test generator covers all RVV extension instructions, 7 new CSRs and diverse configuration parameters, especially due to the combinations of distinct RVV parameter configurations like vlen, vsew, vmul, etc. With a given vlen, about 30,000 tests are generated by our test generator.

The introduced test generator has provides the coverage support. We designed the RVV coverage points based on the test coverage points in RISC-V Arch Test for RV64I/M/F/D, and tuned the coverage setting for vector instructions in a fine-grained manner.