2/19 – 2/23

San Francisco, CA

The International Solid-State Circuits Conference (ISSCC) is the foremost global forum for presentation of advances in solid-state circuits and systems-on-a-chip.

Fig.1 Group photo of the winning teams and organizers.

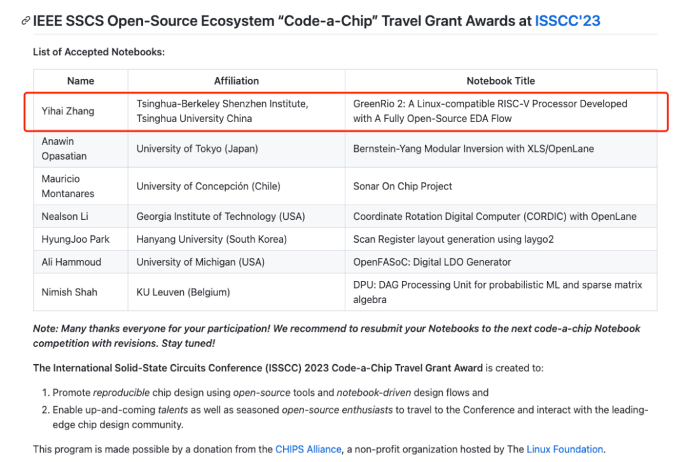

The Code-a-Chip competition was sponsored by the CHIPS Alliance and Google.

The student team of the RISC-V Open Source (RIOS) Lab, is the first place winner in the inaugural international Code-a-Chip competition. They presented their project GreenRio 2 at the ISSCC 2023, along with 6 other design teams from around the world. GreenRio 2 is an open-source Linux-compatible RISC-V processor developed using a complete open-source flow.

Fig.2 “Code-a-chip” winner list

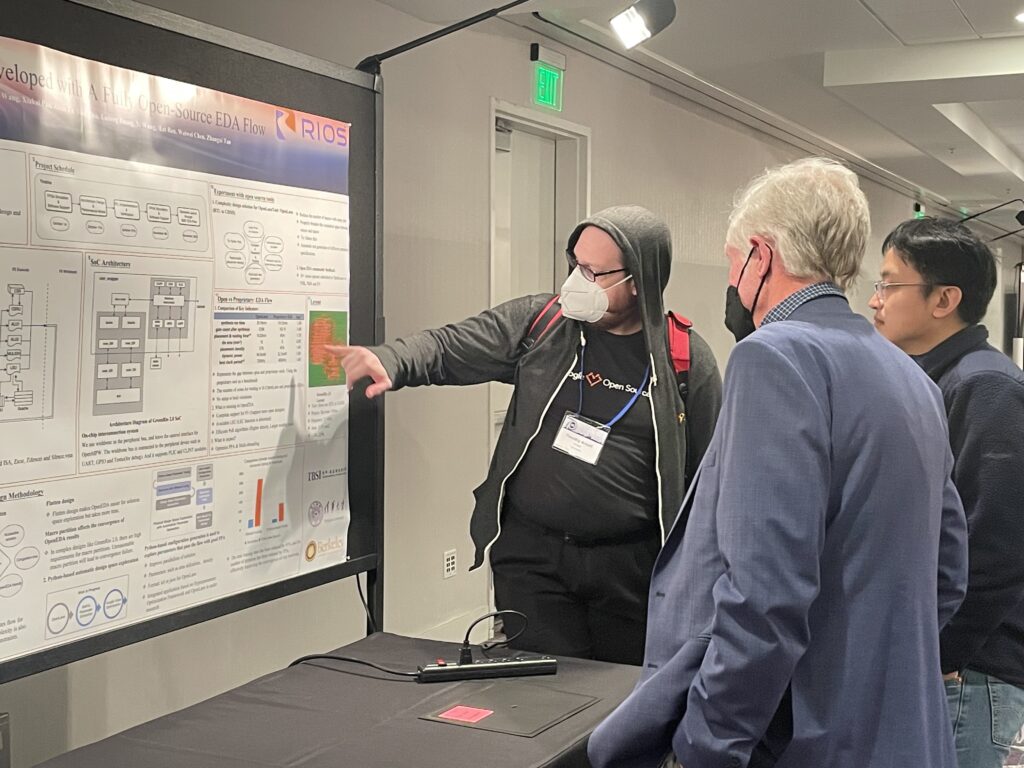

Fig.3 Rob Mains, General Manager, CHIPS Alliance

Tim Ansell, General Manager, Google OpenPDK/EDA

Dr. Zhangxi Tan, Co-director, RIOS Lab

Never before has such a large global community gathered together to come up with a complete open RISC-V instruction set providing a solid foundation for architecture and silicon innovations. With the advent of openEDA and openPDK, building an open microprocessor that can run lots of real software is possible with a pure open-source tool and manufacturing flow.

Because of the maturity and limited support of openEDA, many microprocessors taped out in the past 600+ designs on Google OpenMPWs are only 32-bit MCU-class simple processors. RIOS Rio series RISC-V processors (open source under the Apache 2.0 license) on the other hand include all necessary architecture and performance features to run a full 64-bit operating system like Linux and many real-world software.

At ISSCC, RIOS team presented the design of GreenRio 2, and its open-source design flow. GreenRio 2 is an improvement from the previous version 1.0, which has already been validated in the Google/Skywater OpenMPW-7 tapeout November last year. GreeRio 1.0 is already the most complex processor design that has ever been fabricated by all past Google/SkyWater OpenMPW shuttle runs.

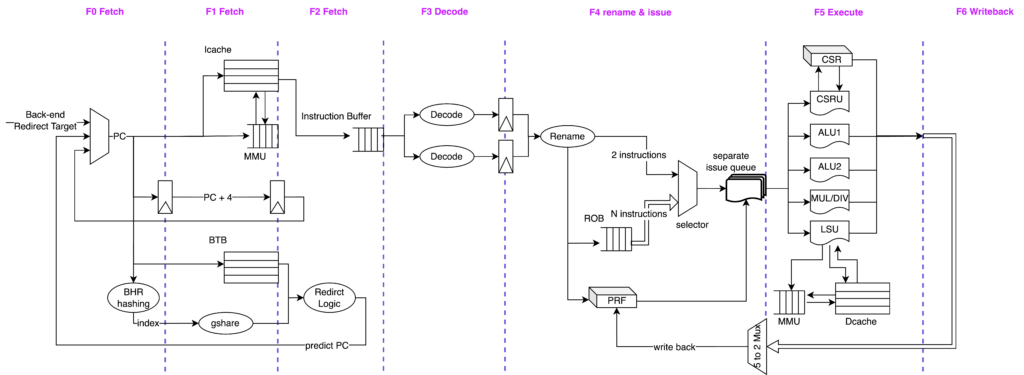

Fig.4 Architecture of GreenRio v2.0

Figure 4 shows the microarchitecture of the GreenRio 2 CPU pipeline. It employs a dual-issue 7-stage out-of-order architecture supporting the RV64ICMA unprivileged RISC-V ISA. It also supports Zicsr, Zifencei and Sfence.vma privileged extensions as well as the S, M and U privilege mode. GreenRio 2 is written in openEDA friendly synthesizable Verilog.

Synthesized with the latest version of OpenLane, the gate count of a single GreenRio 2.0 CPU pipeline is slightly over 230K on the Skywater 130nm process. The area is 15.87 mm^2 at a frequency of 25 MHz.

With the close collaboration between RIOS and Google along with helps from the OpenEDA tool community, GreenRio 2 pushes the design complexity limit that OpenMPW and OpenEDA flow can handle. It is also a very meaningful project demonstrating building a high-performance processor with complete open-source technologies from architecture, RTL to GDSII possible.

Recommended Reading